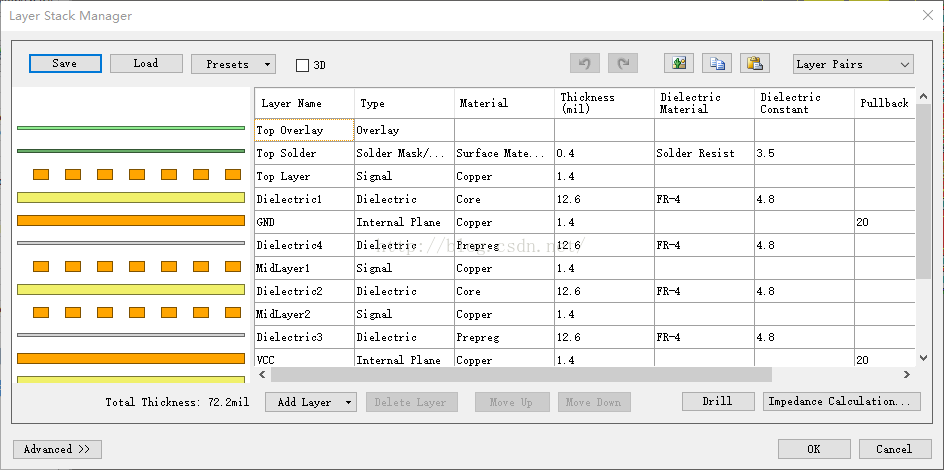

在 Design–Layer Stack Manager–thickness

可以看出你的板子的厚度。 ps:单位计算 100mil = 2.54mm

一般没有要求的话,通常做1.6mm厚度,这样的强度适中;如果强度要大一点,可以采用2.0mm;

除此以外,可以增至5mm左右,薄至0.1mm左右,看实际PCB情况;

1. 确定PCB板叠层结构

2. 从PCB厂家获得工艺能力参数,比如下表(很多参数,只列举部分):

| 基材 | FR4(阻燃环氧玻璃布基覆铜箔板);高频板(聚四氟乙稀材料);江苏泰兴的高频板:

Rogers4350;rogers4403;arlon;teflon |

其他特殊材料工艺应进行工艺评审 |

| 铜箔厚度 | 18um 、35 um 、70 um | 对应基铜厚要满足最小线宽要求, |

| 常用覆铜板规格 | 0.13 1/1, 0.13 H/H,0.21 1/1,0.25 1/1 ,0.36 1/1,0.51 1/1,0.71 1/1,1.0 1/1,1.2 1/1,1.6 H/H,1.6 1/1,1.6 2/2,2.0 1/1,2.0 2/2,2.5 1/1,3.0 1/1,3.2 1/1 | |

| 常用半固化片规格 | 7628(0.185mm),2116(0.105mm)1080(0.075mm)

3313(0.095mm) |

括号内为生益半固化片压合后厚度的理论平均值 |

| 最小导线宽度 | 4mil(对18um、35um的基铜) | 局部区域非BGA、SMT区时需评审 |

| 最小导线间距 | 4mil(允许局部3.5mil)(对18um、35um的基铜) | 局部区域非BGA、SMT区时需评审 |

| 最小导线宽与间距 | 5/7mil(2oz的基铜) | |

| 最小线到盘、盘到盘间距 | 3.5mil(18 um ,35 um),5 mil(70 um) | 此极限时线路与焊盘均无法补偿 |

3. 从厂家获得多层板叠层结构,用以确定半固化片pp和core的叠层方案,通常情况下从top到bottom叠层方案如下:pp-core-pp-core-pp-core-pp…-pp。

4. 根据自身设计中所用器件封装及器件特性情况,再结合上表中所列出的最小线宽,间距等参数确定各层走线的width,差分线的width、gap等参数,width、gap等参数设定完成之后,就需要考虑阻抗匹配问题。

5. 阻抗的计算需要借助工具,通常用allegro自身带的计算工具,但如果用盗版的话计算参数不一定准确,推荐使用polar。

6. 有了线宽、间距和介电常数,就可以综合考虑copper厚度、core的厚度、pp的厚度等参数,不过通常情况,这些参数每家公司都有自己的积累,直接在其之上修改即可

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END

请登录后查看评论内容